电源完好性规划【硬件干货】

时间: 2024-11-22 10:57:03 | 作者: mile体育米乐/电流探头

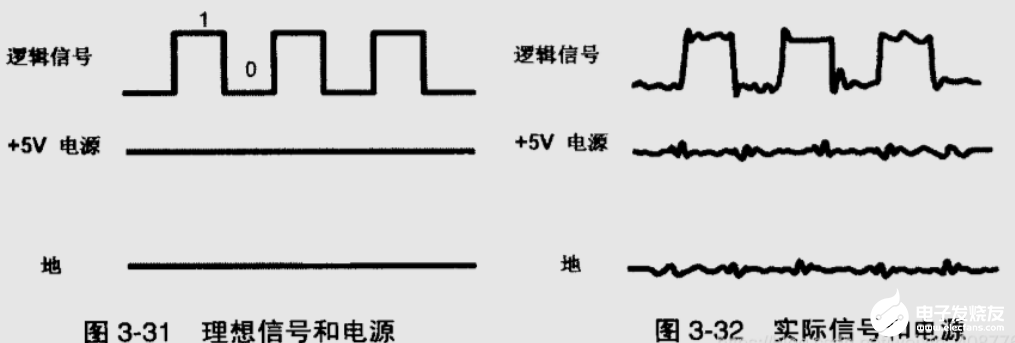

网络考虑,消除 / 下降噪声对电源的影响。电源完好性的规划方针是把电源噪声控制在运转的规模内,为供给洁净安稳的电压,并使它可以维持在一个很小的容差规模内(一般为 5% 以内),实时呼应负载对

很多的芯片引脚在进行逻辑状况切换时,会有一个大的瞬态电流流过回路,形成地平面的动摇,会形成芯片的地与体系地不一致,称为地弹;形成芯片和体系的电源有差压,称为电源弹。在进行PCB叠层规划时,尽可能增大电源平面叠层之间的笔直间隔,削减电源平面和地平面之间的笔直间隔。

重视过孔、走线和电源平面的通流才能;当在一个平面上安置多个电源时,有必要进行电源平面的切割,切割办法要简练合理,切割区域的巨细要满意载流才能的要求;

重视去耦电容的规划,电容的去耦效果是有必定的间隔要求的,即去耦半径。电容焊盘的扇出办法引荐选用多过孔的办法。

重视同步开关噪声(SSN,地弹和电源弹)的影响,可增加去耦电容;在满意体系全体功能需求前提下,尽可能运用陡峭的驱动信号(减缓驱动器的上升沿和下降沿时刻)

纹波:呈现在输出端子间的一种与输入频率和开关频率同步的成分,用有效值表明,一般在输出电压的 0.5% 以下

噪声:呈现在输出端子间的纹波以外的一种高频成分,也用峰 - 峰(peak to peak)值表明,一般在输出电压的 1% 以下

纹波噪声:两者组成,用峰 - 峰(peak to peak)值表明,要求一般在输出电压的 2% 以下

纹波:选用地线环靠接丈量法(靠接丈量),示波器设置带宽(bandwidth)为 20MHz,直流偏置电压(offset)为上面电压精度丈量值。

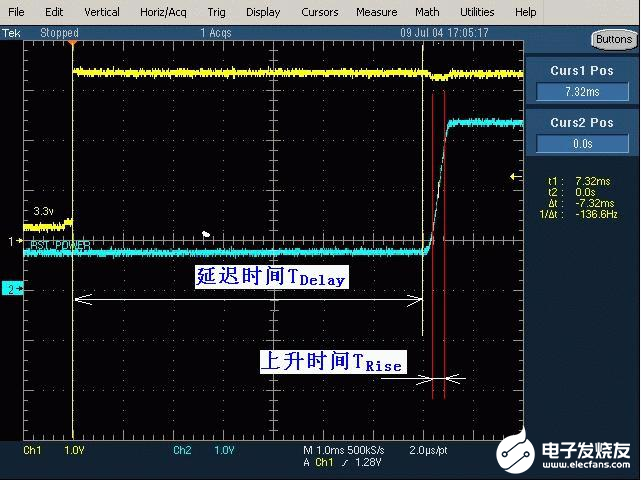

测验办法:示波器设置为上升 / 下降沿触发,开关电源调查上下电波形,能完好显现出来以看出问题

电源输出端电压上下电过冲一般要求不超越被测电压的 10%。在芯片前端测验时,可参阅电平通用规范

电源上电时电压不得有很大的下跌,下电时不能有很大的反冲和回勾(下跌和反冲不能跨过芯片发动作业电压),如呈现台阶现象需求评价影响。

上升时刻(,输出电压从 10% 上升到 90% 的时刻):要求其规模越小越好,但一起要求冲击电流满意合格规范

冲击电流:同上。上电冲击电流最好在冷机时测验(冲击电流最大);下电冲击电流最好在单板满载时进行

测验冲击电流,需求取下理性元件如电感,由于理性器材自身就具有按捺冲击电流的效果。

测验办法:用测验电源输出电流的办法,测验冗余电源的每路电流的输出值,比较每路输出电流的巨细

合格规范:体系电源、其冗余电源(均流)的各路电流输出值相差 10% 以下

要求的契合程度。相同,关于同一体系中的同一个器材,假如指定的端口不同,那么对正常作业的

? SI 仅仅针对高速信号的部分,这样的了解没问题。假如进步认知,将SI 以大类来看,SI&PI&EMI 三者的联系:所以,基础知识系列里仍是

仿真剖析 /

剖析与规划 /

的仿真 /

(Signal Integrity)功能测验方面的作业的时分,对方总是一脸蒙B

? /

后摩尔年代的立异:在米尔FPGA上完成Tiny YOLO V4,助力AIoT运用

全志T113双核异构处理器的运用根据Tina Linux5.0——RTOS体系定制开发

嵌入式学习-飞凌嵌入式ElfBoard ELF 1板卡-LCD显现图片编程示例之介绍mmap